Mae DAPLINK yn disodli'r efelychydd lawrlwythwr llosgydd JLINK OBSTLINK STM32 ARM

Nodweddion cynnyrch

(1) Mae PCB sgematig caledwedd yn gwbl ffynhonnell agored, meddalwedd ffynhonnell agored, dim risg hawlfraint.

Ar hyn o bryd, mae'r jlink/stlink ar y farchnad yn cael eu lladrata, ac mae rhai problemau cyfreithiol yn eu defnyddio. Pan ddefnyddir rhywfaint o jlink gydag IDE fel MDK, bydd yn ysgogi lladrata ac ni ellir ei ddefnyddio'n normal, ac mae gan rai fersiynau o jlink y broblem o golli cadarnwedd ar ôl ei ddefnyddio am gyfnod o amser. Unwaith y bydd y cadarnwedd wedi'i golli, mae angen i chi adfer y feddalwedd â llaw.

(2) Arwain rhyngwyneb SWD, cefnogi meddalwedd dadfygio PC prif ffrwd, gan gynnwys keil, IAR, openocd, cefnogi lawrlwytho SwD, dadfygio cam sengl.

(3) Gall rhyngwyneb JTAG, gydag openocd, gefnogi dadfygio bron pob sglodion SoC ledled y byd, fel cyfres ARM Cortex-A, DSP, FPGA, MIPS, ac ati, oherwydd mai dim ond protocol preifat a ddiffinnir gan ARM yw'r protocol SWD, a JTAG yw'r safon ryngwladol IEEE 1149. Y sglodion targed efelychydd arferol fel arfer yw cyfres ARM Cortex-M, nad yw'n cyflwyno rhyngwyneb JTAG, ac mae'r cynnyrch hwn yn cyflwyno rhyngwyneb JTAG, sy'n addas i chi ddatblygu a dadfygio gwaith o dan lwyfannau eraill.

(4) Cefnogi porthladd cyfresol rhithwir (hynny yw, gellir ei ddefnyddio fel efelychydd neu fel offeryn porthladd cyfresol, gan ddisodli ch340, cp2102, p12303)

(5) Mae DAPLink yn cefnogi uwchraddio cadarnwedd gyriant fflach USB, dim ond daearu'r nRST, plygio i mewn i DAPLink, PC. Bydd gyriant fflach USB, dim ond llusgo'r cadarnwedd newydd (ffeil hecs neu bin) i'r gyriant fflach USB i gwblhau'r uwchraddiad cadarnwedd. Gan fod DAPLink yn gweithredu llwythwr cychwyn gyda swyddogaeth disg U, gall gwblhau'r uwchraddiad cadarnwedd yn hawdd. Os oes gennych gynnyrch sy'n seiliedig ar STM32 mewn cynhyrchu màs, ac efallai y bydd angen uwchraddio'r cynnyrch yn ddiweddarach, mae'r cod llwythwr cychwyn yn DAPLink yn haeddu eich cyfeirio, nid oes angen i'r cleient osod IDE cymhleth na llosgi offer i gwblhau'r uwchraddiad, dim ond llusgo i'r ddisg U all gwblhau uwchraddiad eich cynnyrch yn gyfleus.

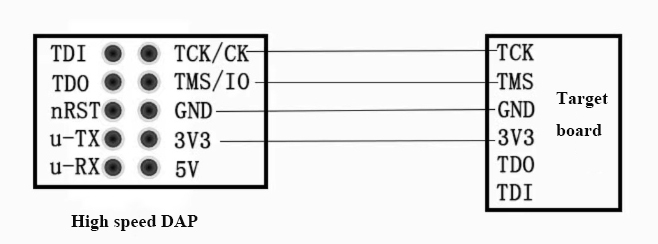

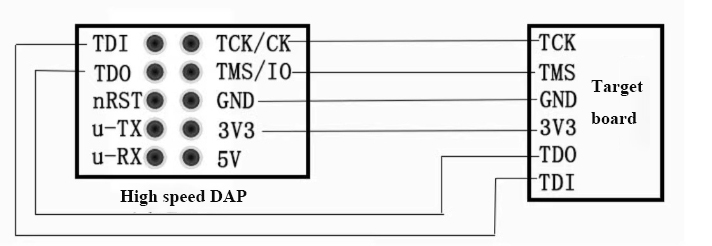

Gweithdrefn gwifrau

1. Cysylltwch yr efelychydd â'r bwrdd targed

Diagram gwifrau SWD

Diagram gwifrau JTAG

C&A

1. Methiant llosgi, sy'n dynodi GWALL RDDI-DAP, sut i'w ddatrys?

A: Gan fod cyflymder llosgi'r efelychydd yn gyflym, bydd y signal rhwng y llinell dupont yn cynhyrchu croestalk, ceisiwch newid y llinell Dupont fyrrach, neu'r llinell Dupont sydd â chysylltiad agos, gallwch hefyd geisio lleihau'r cyflymder llosgi, yn gyffredinol gellir datrys hyn yn normal.

2. Beth ddylid ei wneud os na ellir canfod y targed, sy'n dynodi methiant cyfathrebu?

A: Gwiriwch yn gyntaf a yw'r cebl caledwedd yn gywir (GND, CLK, 10, 3V3), ac yna gwiriwch a yw cyflenwad pŵer y bwrdd targed yn normal. Os yw'r bwrdd targed yn cael ei bweru gan yr efelychydd, gan mai dim ond 500mA yw cerrynt allbwn uchaf yr USB, gwiriwch a yw cyflenwad pŵer y bwrdd targed yn annigonol.

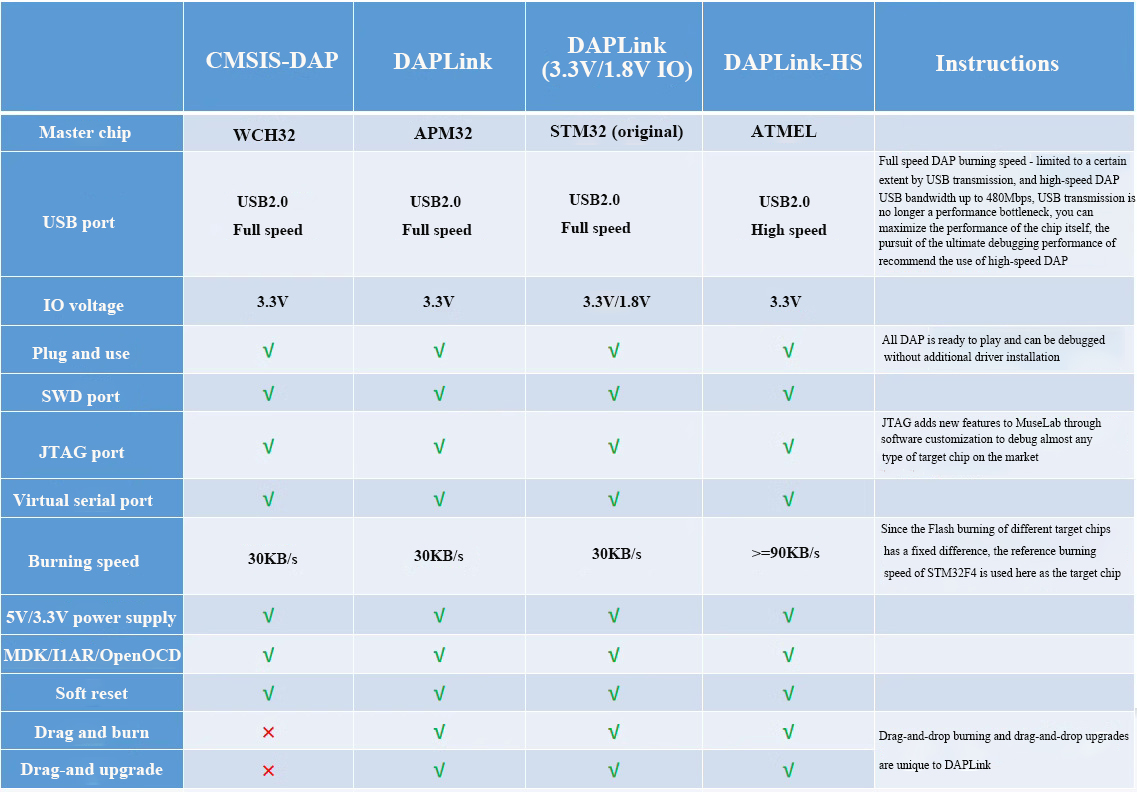

3. Pa losgi dadfygio sglodion sy'n cael ei gefnogi gan CMSIS DAP/DAPLink?

A: Y senario defnydd nodweddiadol yw rhaglennu a dadfygio'r MCU. Yn ddamcaniaethol, gall cnewyllyn y gyfres Cortex-M ddefnyddio DAP ar gyfer llosgi a dadfygio, sglodion nodweddiadol fel sglodion cyfres lawn STM32, cyfres lawn GD32, cyfres nRF51/52 ac yn y blaen.

4. A allaf ddefnyddio efelychydd DAP ar gyfer dadfygio o dan Linux?

A: O dan Linux, gallwch ddefnyddio openocd ac efelychydd DAP ar gyfer dadfygio. openocd yw'r dadfygiwr ffynhonnell agored mwyaf poblogaidd a phwerus yn y byd. Gallwch hefyd ddefnyddio openocd o dan Windows, trwy ysgrifennu'r sgript ffurfweddu priodol gallwch gyflawni dadfygio'r sglodion, llosgi a gweithrediadau eraill.

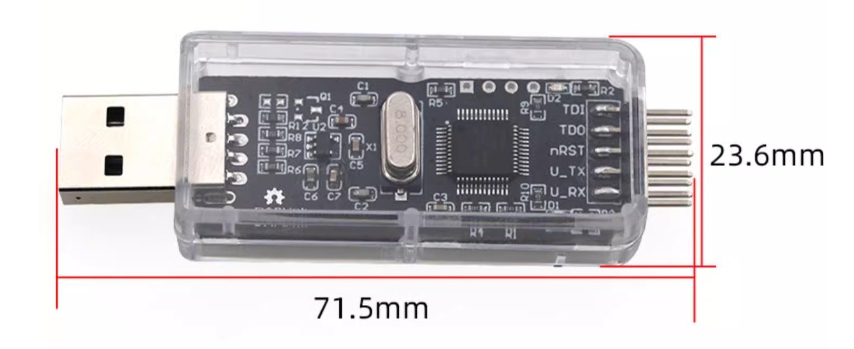

Saethu cynnyrch

Categorïau cynhyrchion

-

Ffôn

-

E-bost

-

Whatsapp

-

Skype

-

Skype

-

Skype