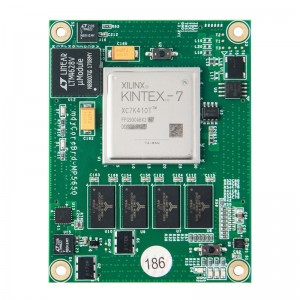

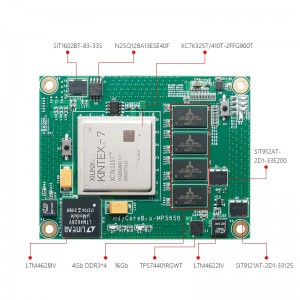

FPGA XILINX-K7 KINTEX7 XC7K325 410T Gradd ddiwydiannol

DDR3 SDRAMQ: 16GB DDR3, 4GB y darn, Data Bit Data 16bit SPI Flash: Un darn o 128MBITQSPIFLASH, y gellir ei ddefnyddio ar gyfer ffeiliau ffurfweddu FPGA a storio data defnyddwyr Lefelau rhyngwyneb Banc FPGA: addasadwy 1.8V, 2.5V, 3.3V trydanol Os oes angen i chi ddisodli'r lefel, dim ond angen i chi ddisodli safle cyfatebol y gleiniau magnetig i gyflawni addasiad. Cyflenwad pŵer bwrdd craidd: ystod 5V-12V o gyflenwad pŵer EEPROM; Mae M24C02-WMN6TP yn seiliedig ar ddyfais bws I2C. Yn dilyn dull cychwyn bwrdd craidd y protocol ail linell: yn cefnogi dau ddull cychwyn, sef cysylltwyr JTAG, QSPI Flash. Porthladd estynedig, 120pin, rhyngwyneb SFP plât gwaelod Panasonic AXK5A2137yg MP5700: gall 2 fodiwl optegol gyflawni cyfathrebu ffibr optegol cyflym, mor uchel â 6GB/s cloc plât gwaelod: 1 cloc cyfeirio 200MHz wedi'i gysylltu â throed tiwb cloc MRCC y bwrdd craidd, 1 125MHz Mae plât gwaelod traed tiwb cloc GTX y cloc wedi'i gysylltu â'r bwrdd craidd yn borthladd ehangu 40 -pin: cadwch borthladd estyniad 40 -ergyd gyda bylchau safonol o 2.54mm, a ddefnyddir i gysylltu modiwl dylunio'r cwsmer ei hun. Cloc bwrdd Essence Core: mae sawl ffynhonnell cloc ar y bwrdd. Mae'r rhain yn cynnwys y cloc system 200MHz, y cloc GTX 125MHz, a'r cloc EMCCLK 66MHz. Porthladd JTAG: 10 pwyth porthladd JTAG safonol 2.54mm, ar gyfer lawrlwytho a dadfygio LEDs ar gyfer rhaglenni FPGA: cyfanswm o 6 golau LED coch yn y bwrdd craidd, sy'n nodi cyflenwad pŵer cerdyn y bwrdd, 4 golau dangosydd signal a thraed tiwb IO FPGA wedi'u cysylltu'n uniongyrchol Allwedd: 4 allwedd. 4 allwedd. Nhw yw botymau ailosod FPGA, allweddi Program_b a dau allwedd defnyddiwr.

Mae'r FPGA Xilinx-K7 Kintex7 XC7K325 410T yn fodel penodol o FPGA (Field-Programmable Gate Array) a ddatblygwyd gan Xilinx. Dyma rai manylion allweddol am yr FPGA hwn:Cyfres: Kintex-7: Mae FPGAs cyfres Kintex-7 Xilinx wedi'u cynllunio ar gyfer cymwysiadau perfformiad uchel ac maent yn cynnig cydbwysedd da rhwng perfformiad, pŵer a phris.Dyfais: XC7K325: Mae hyn yn cyfeirio at y ddyfais benodol o fewn y gyfres Kintex-7. Mae'r XC7K325 yn un o'r amrywiadau sydd ar gael yn y gyfres hon, ac mae'n cynnig manylebau penodol, gan gynnwys capasiti celloedd rhesymeg, sleisys DSP, a chyfrif Mewnbwn/Allbwn.Capasiti Rhesymeg: Mae gan yr XC7K325 gapasiti celloedd rhesymeg o 325,000. Blociau adeiladu rhaglenadwy mewn FPGA yw celloedd rhesymeg y gellir eu ffurfweddu i weithredu cylchedau a swyddogaethau digidol.Sleisys DSP: Adnoddau caledwedd pwrpasol o fewn FPGA yw sleisys DSP sydd wedi'u optimeiddio ar gyfer tasgau prosesu signalau digidol. Gall union nifer y sleisys DSP yn yr XC7K325 amrywio yn dibynnu ar yr amrywiad penodol. Cyfrif Mewnbwn/Allbwn: Mae'r "410T" yn rhif y model yn dangos bod gan yr XC7K325 gyfanswm o 410 o binnau Mewnbwn/Allbwn defnyddwyr. Gellir defnyddio'r pinnau hyn i ryngwynebu â dyfeisiau allanol neu gylchedwaith digidol arall. Nodweddion Eraill: Gall fod gan yr FPGA XC7K325 nodweddion eraill, megis blociau cof integredig (BRAM), trawsderbynyddion cyflymder uchel ar gyfer cyfathrebu data, ac amrywiol opsiynau ffurfweddu. Mae'n bwysig nodi bod FPGAs fel y Xilinx-K7 Kintex7 XC7K325 yn ddyfeisiau rhaglenadwy sy'n eich galluogi i weithredu cylchedau a swyddogaethau digidol personol trwy raglennu eu celloedd rhesymeg. Mae'r hyblygrwydd hwn yn eu gwneud yn addas ar gyfer ystod eang o gymwysiadau, gan gynnwys cyfrifiadura perfformiad uchel, prosesu signalau digidol, a chyflymiad caledwedd.

Categorïau cynhyrchion

-

Ffôn

-

E-bost

-

Whatsapp

-

Skype

-

Skype

-

Skype